3D Memory

(C) KnowMade

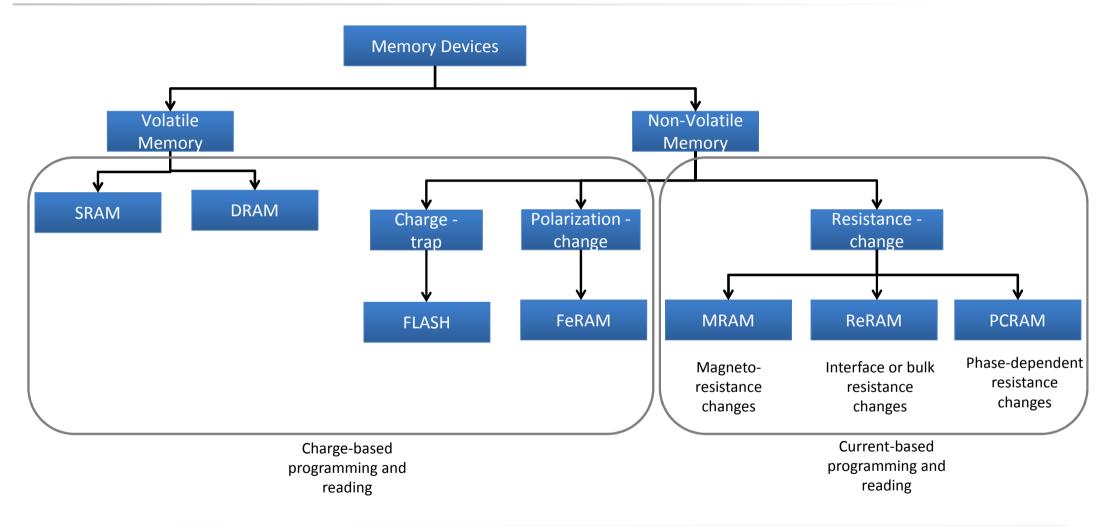

Memory Types

3

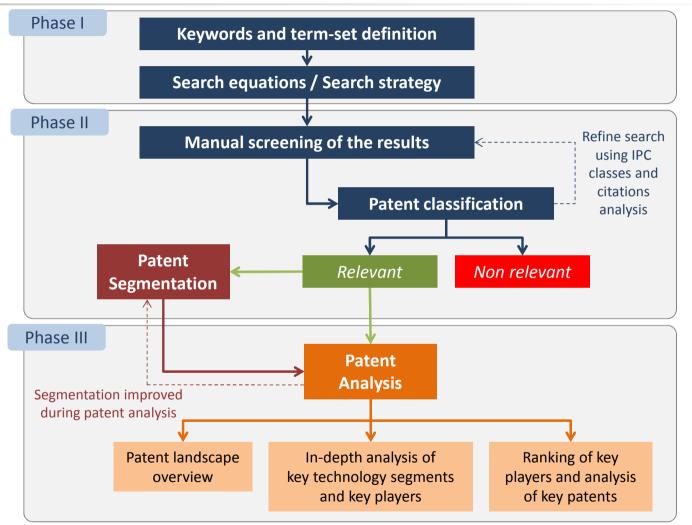

Methodology for patent search, selection and analysis

4

### **TABLE OF CONTENT**

3D Memory

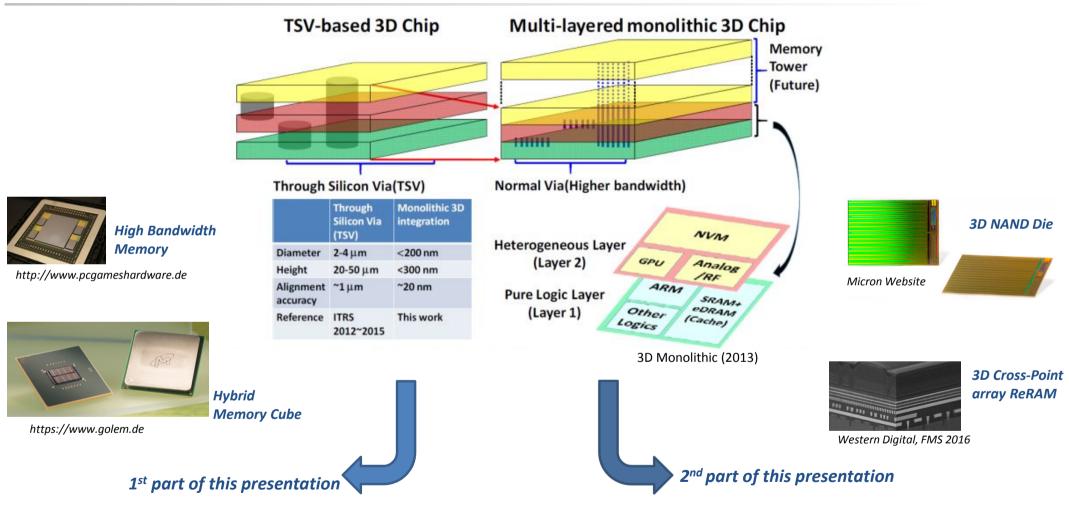

**TSV Stacked Memory**

3D NVM

Conclusion

**KnowMade**

3D Memory – Patent Landscape Analysis | D43D Workshop June 2017 © 2017 All rights reserved | www.knowmade.com

#### **TABLE OF CONTENT**

3D Memory

# **TSV Stacked Memory**

3D NVM

Conclusion

**KnowMade**

3D Memory – Patent Landscape Analysis | D43D Workshop June 2017 © 2017 All rights reserved | www.knowmade.com

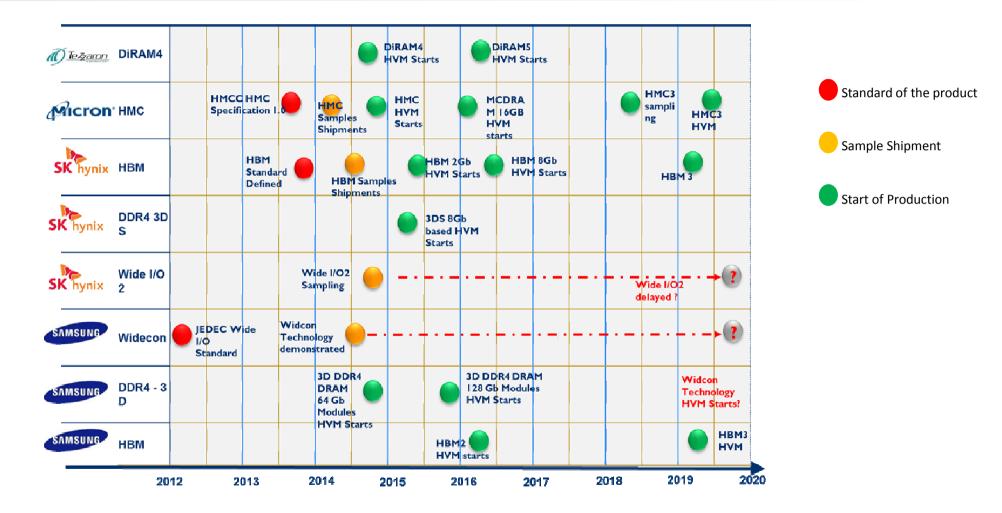

#### **INTRODUCTION** TSV Stacked Memory Roadmap

**KnowMade**

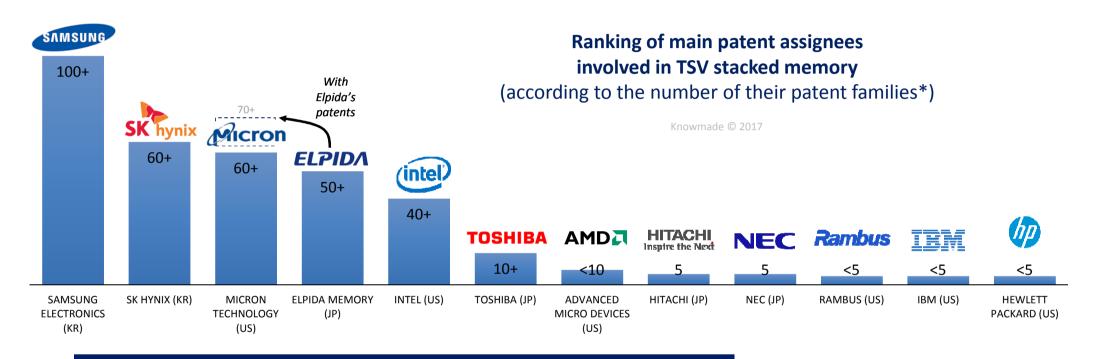

#### **IP OVERVIEW**

Main patent assignees in TSV stacked memory

- Mainly industrial players from USA, Japan and Korea

- Micron/Elpida and Samsung own more than 40% of patents together

- Most of Elpida's patents were acquired by PS4 Luxco in 2013

- **R&D Labs** have only few patents (Carnegie Mellon University, University of California, ITRI, ETRI, Hiroshima University)

- Tezzaron holds 6 patent families on 3-dimensional IC design (not focus on stacked memory)

\* A patent family is a set of patents filed in multiple countries to protect a single invention by a common inventor. A first application is made in one country – the priority country – and is then extended to other countries.

### PATENT LANDSCAPE OVERVIEW

Time evolution of patent publications in TSV stacked memory

#### 1,500+ patents grouped in 400+ patent families\* 70 Knowmade © 2017 60 57 53 52 Samsung Number of publications 50 6.4% CAGR 2005-2012 SK Hynix 44 Micron 42 IBM 40 Elpida US5099309 34 Three-Intel dimensional memory card 28 30 Toshiba structure with internal 25 direct chip attachment Other Assignees 20 16 12 10 1 0 1990 1991 1992 1993 1994 1995 1996 1997 1998 1999 2000 2001 2002 2003 2004 2005 2006 2007 2008 2009 2010 2011 2012 2013 2014 2015 2016

Patenting activity in TSV stacked memory

Earliest Publication Year of Each Patent Family

\* A patent family is a set of patents filed in multiple countries to protect a single invention by a common inventor.

A first application is made in one country - the priority country - and is then extended to other countries.

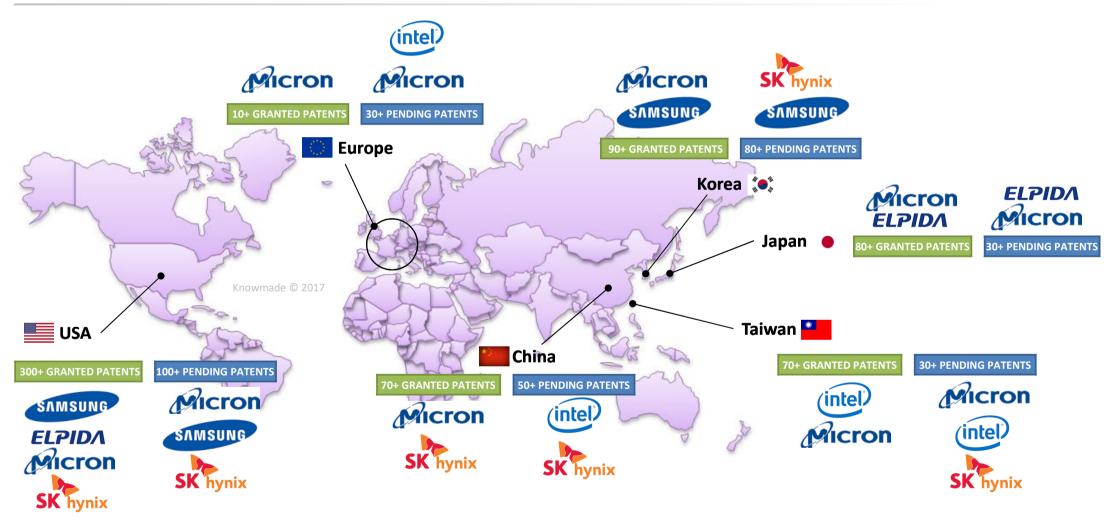

#### PATENT LANDSCAPE OVERVIEW

Geographic map of patenting activity of main IP players involved in TSV stacked memory

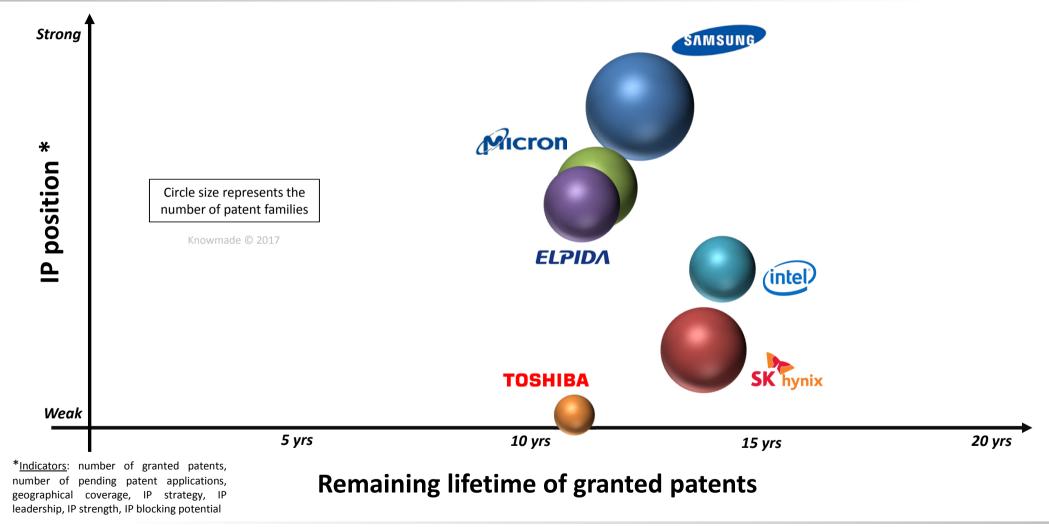

## **IP POSITION OF MAIN PATENT ASSIGNEES**

IP position vs. remaining lifetime of enforceable patents

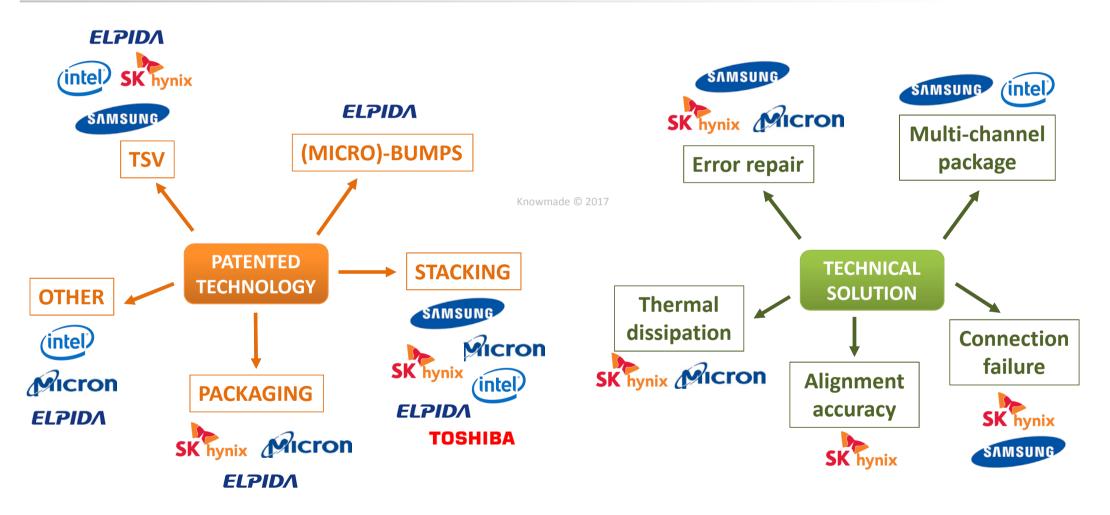

#### **PATENT SEGMENTATION**

Technologies patented by key IP players in TSV stacked memory

12

## TECHNOLOGY OVERVIEW

#### Technologies patented by key IP player in TSV stacked memory

#### Patented technologies used in SK Hynix HBM's package The 4 DRAM dies are connected together with TSV & micro-bumps US9257413 (2015) Outer connection terminals 550 **SYSTEMPLUE** 310 $\rightarrow$ plurality of solder balls 2D arrayed. DRAM Die Micro-humn US8592952 (2013) $\rightarrow$ area of a surface on which the ✓ Diameter 16µm **Reduce** misalignment ✓ Pitch 40µm outer connection terminals are 23 103 between chips Underfill arraved can be maximized (even ✓ Thickness 19µn 22 $\rightarrow$ magnetic force applied though a width of the lower TSV -12 between the align patterns semiconductor chip is reduced) 52a ✓ Diameter 6µm 21 51b 101 Depth 46.5um ✓ Pitch 40µm RAM Die Intermediate front side bumps 290 Micro-bump $\rightarrow$ front side bump body 291 (Cu) Diameter 20um DRAM Di ✓ Pitch 55µm contacting the chip contact portion 235 Underfill Logic Die ✓ Thickness 33µm $\rightarrow$ wetting layer 293 (Ni) stacked on the front side bump body 291. US9390997 (2015) Flip-Chip Bump Connection electrodes 160 ✓ Size 100µm ✓ Pitch 200µm and 162 (front bumps and rear Lower backside bumps 180 -310 $\rightarrow$ Include also oxidation resistant bumps) $\rightarrow$ formed of any one of solder. layer 185(Au) nickel, copper, tin and alloy Conductive adhesives 295 (solder thereof HBM Package Cross Section, SEM View, System Plus Consulting lavers) $\rightarrow$ disposed on the respective wetting 180(183-Connection member 164 1.40 ---- $\rightarrow$ solder having a low melting layers 293 -110 $\rightarrow$ combined with the lower backside point or an anisotropic conductive film (ACF) including bumps resin and fine conductive balls

#### 3D Memory – Patent Landscape Analysis | D43D Workshop June 2017 © 2017 All rights reserved | www.knowmade.com

####

#### CONCLUSION

#### Patent Landscape analysis TSV Stacked Memory

| Top-5 patent<br>assignees           | SAMSUNG                                                                                                 |                                                                                                        | SK hynix                                                                                                                                             | TOSHIBA                                                                                             | (intel)                                                    |  |

|-------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------|--|

| IP position                         | Very Strong                                                                                             | Strong                                                                                                 | Low                                                                                                                                                  | Very Low                                                                                            | Medium                                                     |  |

| Main countries of<br>patent filings | USA<br>Korea                                                                                            | Worldwide                                                                                              | USA                                                                                                                                                  | USA<br>Japan                                                                                        | USA<br>Taiwan                                              |  |

| Main patented<br>technology         | Control of the stack,<br>Wafer to wafer technique                                                       | Memory technology improvement,<br>Interconnection stacking                                             | Stacking Issues: dissipation,<br>adhesion,                                                                                                           | Stacking Issues                                                                                     | Method for accessing memory,<br>Thinner package substrates |  |

| Main technical issues in patents    | Connection Failure<br>Multi-Channel Package<br>Error Repair                                             | Thermal Dissipation<br>Error Repair                                                                    | Alignment Accuracy<br>Error Repair<br>Thermal Dissipation<br>Connection Failure                                                                      | Alignment Accuracy<br>Connection Failure                                                            | Multi-Channel Package<br>Alignment Accuracy                |  |

| Products                            | 3D DDR4 DRAM production in 2014,<br>HBM2 4Gb and 8Gb in 2016                                            | Production of 16Gb HMC Gen2 in<br>2014 with Intel                                                      | Production of HBM1 2Gb in 2014,<br>Production of 3DS DDR4 8Gb and<br>Wide I/O2 in 2015,<br>Production of HBM2 4Gb and 8Gb in<br>2016<br>HBM3 in 2020 | In 2017/2018, 1To package of 16<br>NAND dies TSV stacked<br>2To package will be proposed in<br>2019 | Production of 16Gb HMC Gen2 in<br>2014 with Micron         |  |

| Patent litigations                  | Nov-2014<br>ELM 3D as plaintiff for patent<br>infringement against Samsung<br>Final Decision in Q2 2017 | Nov-2014<br>ELM 3D as plaintiff for patent<br>infringement against Micron<br>Final Decision in Q2 2017 | Nov-2014<br>ELM 3D as plaintiff for patent<br>infringement against SK Hynix<br>Final Decision in Q2 2017                                             | No                                                                                                  | No                                                         |  |

#### **TABLE OF CONTENT**

3D Memory

**TSV Stacked Memory**

## 3D NVM

Conclusion

3D Memory – Patent Landscape Analysis | D43D Workshop June 2017 © 2017 All rights reserved | www.knowmade.com

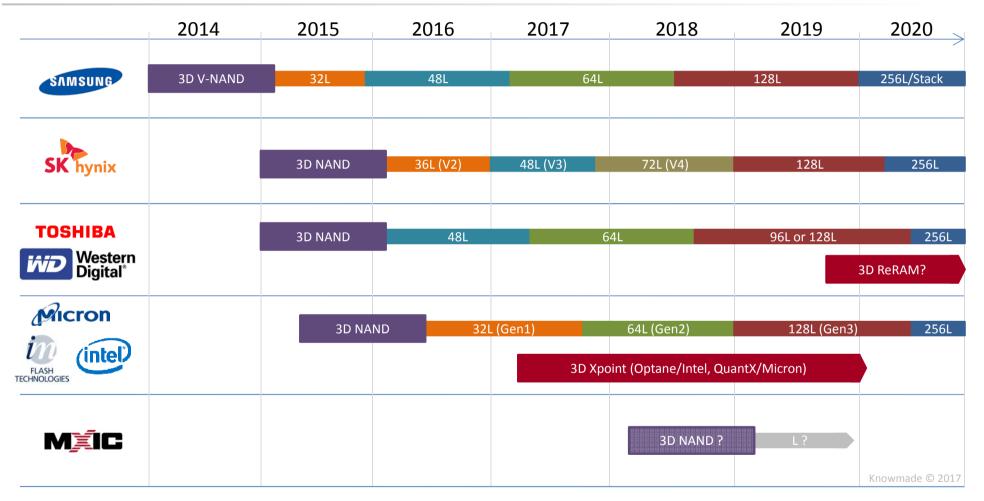

3D NVM Roadmap

**KnowMade**

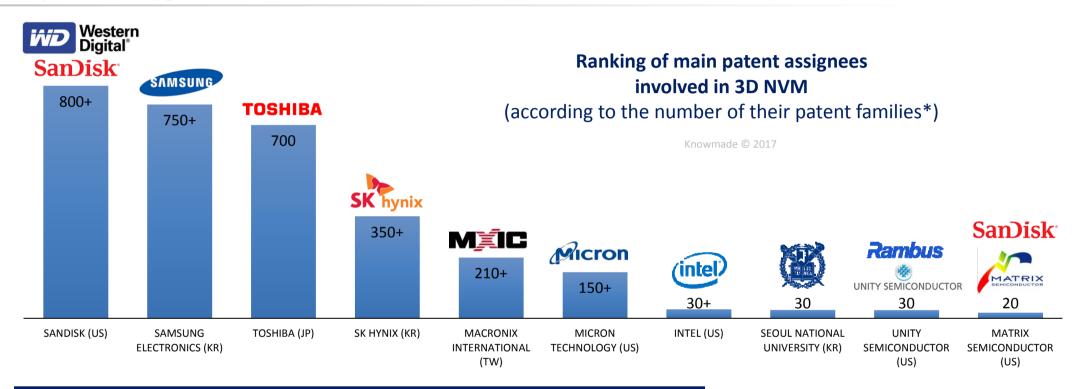

### **IP OVERVIEW**

Main patent assignees in 3D NVM

- Mainly industrial players from USA, Korea, Japan and Taiwan

- Top 3: SanDisk/Western Digital, Samsung and Toshiba own more than 65% of patents together

- Western Digital acquired SanDisk in 2016

- **R&D Labs** have only few patents (Seoul National University)

- Rambus acquired Unity Semiconductor in 2012

- SanDisk acquired Matrix Semiconductor in 2005

\* A patent family is a set of patents filed in multiple countries to protect a single invention by a common inventor. A first application is made in one country – the priority country – and is then extended to other countries.

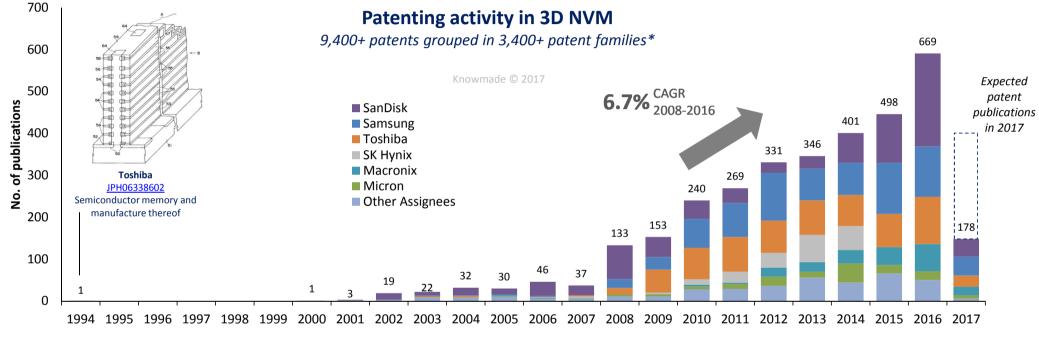

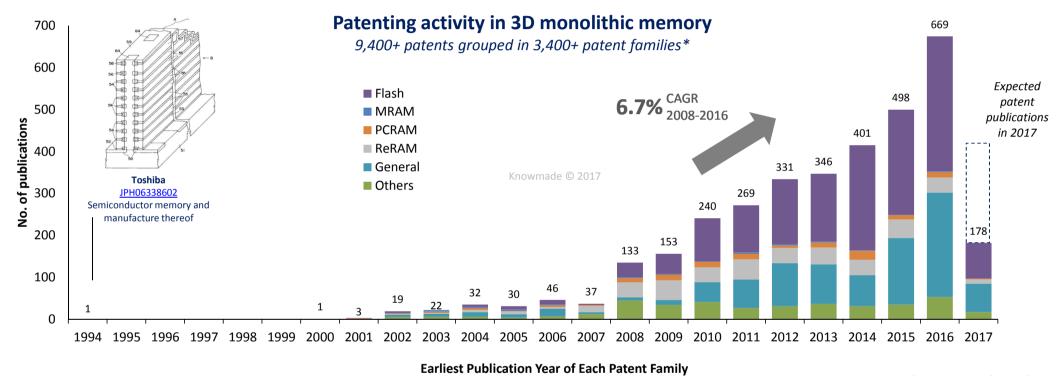

#### **IP OVERVIEW** Time evolution of patent publications in 3D NVM

**Earliest Publication Year of Each Patent Family**

<u>Note</u>: The patent search was done in June 2017, thus the data corresponding to the year 2017 are not complete. At the time of the patent search, 178 patent families had been published in 2017.

\* A patent family is a set of patents filed in multiple countries to protect a single invention by a common inventor.

A first application is made in one country - the priority country - and is then extended to other countries.

#### **IP OVERVIEW**

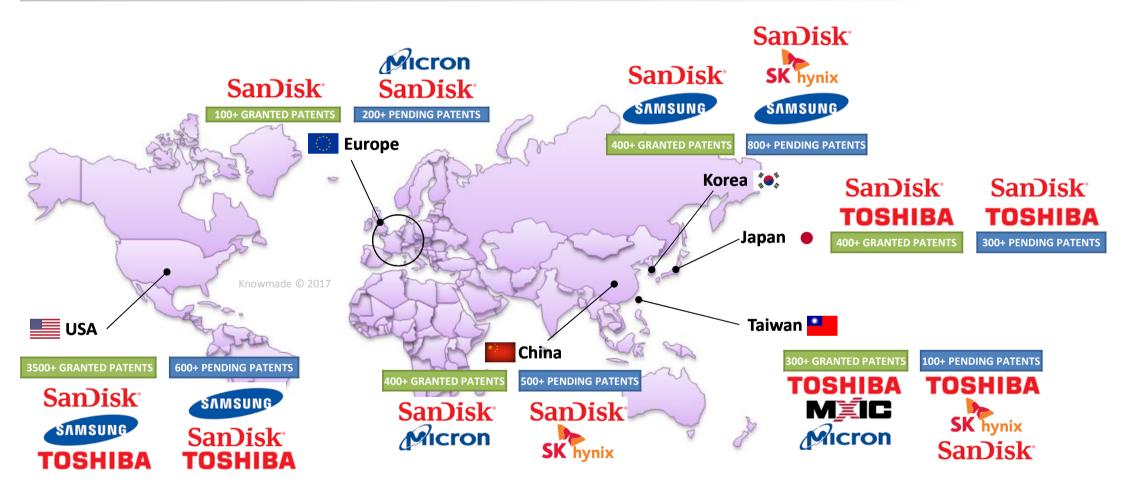

Geographic map of patenting activity of main IP players involved in 3D NVM

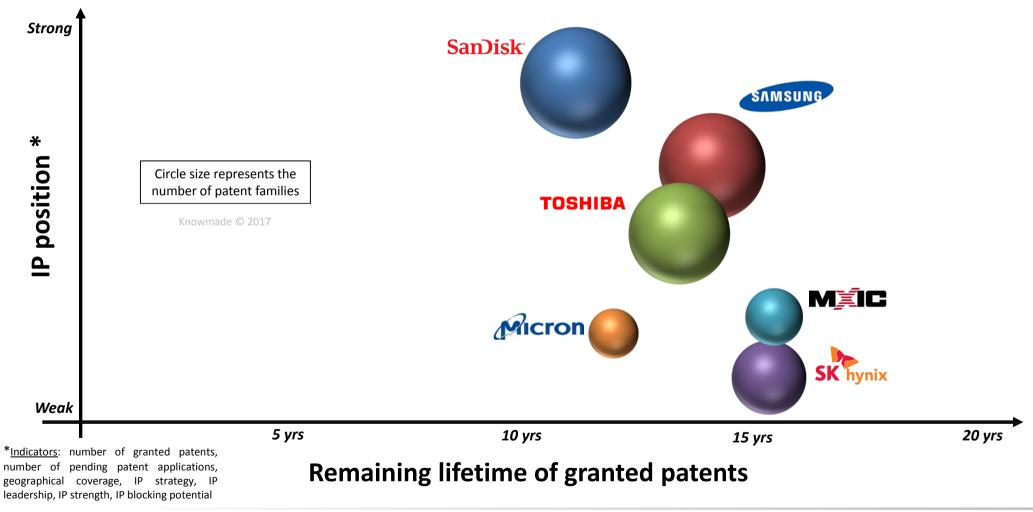

## **IP POSITION OF MAIN PATENT ASSIGNEES**

IP position vs. remaining lifetime of enforceable patents

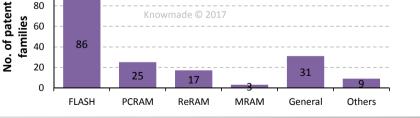

### **PATENT SEGMENTATION**

Memory types timeline of publication in 3D NVM

<u>Note</u>: The patent search was done in June 2017, thus the data corresponding to the year 2017 are not complete. At the time of the patent search, 178 patent families had been published in 2017.

\* A patent family is a set of patents filed in multiple countries to protect a single invention by a common inventor.

A first application is made in one country – the priority country – and is then extended to other countries.

#### **PATENT SEGMENTATION**

Memory types by key IP players in 3D NVM

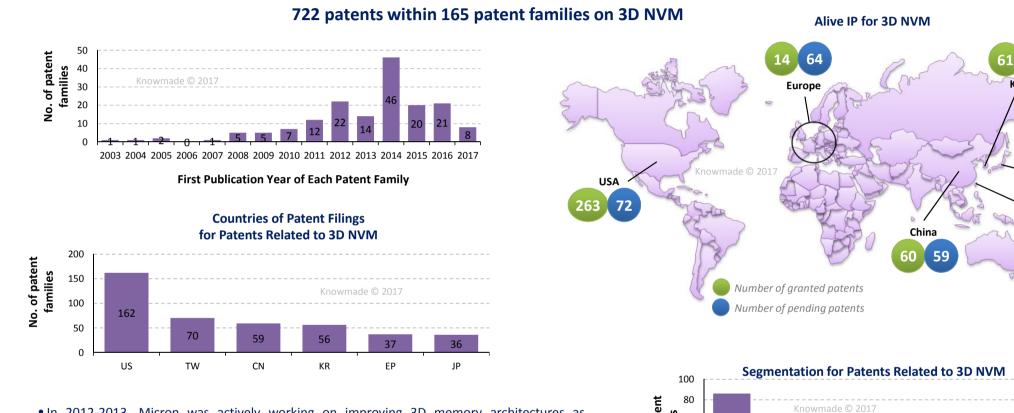

#### **TECHNOLOGY OVERVIEW** Micron Technology IP Portfolio in 3D NVM

• In 2012-2013, Micron was actively working on improving 3D memory architectures as evidenced by the numerous patents published in 2014.

- Half of Micron's patent publications are related to Flash Memories

- Micron doesn't have a worldwide IP strategy in 3D NVM. Indeed, Micron has a very strong IP presence in USA and neglect Europe and Asian countries

ΔΔ

Japan

Taiwan

62

Korea

#### **TABLE OF CONTENT**

3D Memory

## **TSV Stacked Memory**

3D NVM

Conclusion

**KnowMade**

3D Memory – Patent Landscape Analysis | D43D Workshop June 2017 © 2017 All rights reserved | www.knowmade.com

#### CONCLUSION

- First patents related to 3D memory technologies (TSV Stacked or 3D NVM) were published in the 1990s, but patenting activity really started in the 2000s with a strong increase since 2007-2008 and first marketed products appeared in 2014.

- The patent landscape of 3D memories (TSV Stacked or 3D NVM) is led by the microelectronics giants, offering few space for new entrants and heralding inevitable patent battles.

| Top patent<br>assignees<br>IP position | SanDisk<br>Western<br>Digital |                                                           | SAMSUNG                                           |                                                                        | TOSHIBA                                                                                    |                                                           | SK hynix                                                     |                                                                              | MĨC         |                                               | Micron (intel)                                  |                                                                                                |

|----------------------------------------|-------------------------------|-----------------------------------------------------------|---------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------|-------------|-----------------------------------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------|

|                                        | TSV Stacked                   | 3D NVM                                                    | TSV Stacked                                       | 3D NVM                                                                 | TSV Stacked                                                                                | 3D NVM                                                    | TSV Stacked                                                  | 3D NVM                                                                       | TSV Stacked | 3D NVM                                        | TSV Stacked                                     | 3D NVM                                                                                         |

| IP position                            | /                             | Very Strong                                               | Very Strong                                       | Strong                                                                 | Very Low                                                                                   | Medium                                                    | Low                                                          | Very Low                                                                     | /           | Low                                           | Strong                                          | Low                                                                                            |

| Last and<br>future<br>Products         | /                             | 3D NAND<br>64L/512Gb<br>(end 2017)<br>3D ReRAM<br>In 2019 | HBM2 4Gb<br>and 8Gb in<br>2016<br>HBM3 in<br>2020 | 3D V-NAND<br>Gen4<br>64L/512Gb<br>(June 2017)<br>"Z-NAND"<br>prototype | 2017/2018 :<br>1To package<br>of 16 NAND<br>dies TSV<br>stacked,<br>2To package<br>in 2019 | 3D NAND<br>64L/512Gb<br>(end 2017)<br>3D ReRAM<br>In 2019 | Production of<br>HBM2 4Gb and<br>8Gb in 2016<br>HBM3 in 2020 | 3D NAND Gen4<br>72L/256Gb (Q2<br>2017)<br>3D NAND<br>72L/512Gb<br>(end 2017) | /           | 3D-NAND<br>product<br>introduction in<br>2018 | MCDRAM<br>production in<br>2016<br>HMC3 in 2020 | 3D NAND Gen2<br>64L/512Gb<br>(2017)<br>3D Xpoint<br>Optane<br>Intel/QuantX<br>Micron<br>(2017) |

For more informations: <u>www.knowmade.com</u> / contact@knowmade.fr

3D Memory – Patent Landscape Analysis | D43D Workshop June 2017 © 2017 All rights reserved | www.knowmade.com

**KnowMade**

KnowMade SARL 2405 route des Dolines 06902 Sophia Antipolis, France

> www.knowmade.com contact@knowmade.fr